书籍详情

![《数字逻辑与计算机组成》[40M]百度网盘|亲测有效|pdf下载](/uploads/s1/10bb0c7798c58017.jpg)

![《数字逻辑与计算机组成》[40M]百度网盘|亲测有效|pdf下载](/uploads/s1/10bb0c7798c58017.jpg)

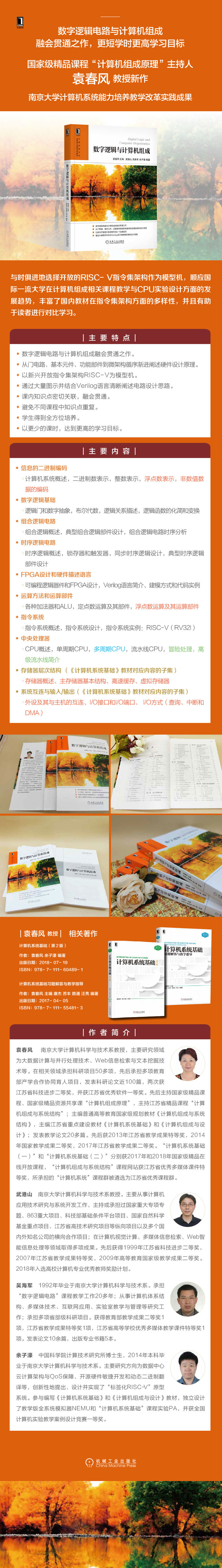

数字逻辑与计算机组成

- 出版社:机械工业出版社自营官方旗舰店

- 出版时间:2020-10

- 热度:11835

- 上架时间:2024-06-30 09:38:03

- 价格:9.1

免责声明

本站支持尊重有效期内的版权/著作权,所有的资源均来自于互联网网友分享或网盘资源,一旦发现资源涉及侵权,将立即删除。希望所有用户一同监督并反馈问题,如有侵权请联系站长或发送邮件到ebook666@outlook.com,本站将立马改正

内容介绍

产品特色

内容简介

数字逻辑与计算机组成一直以来都是相辅相成不可分割的,本书将二者合二为一,更利于加强读者对计算机各组成部件的工作原理的理解以及融会贯通,全书主要内容包括:数据在计算机内部的二进制编码表示;数字逻辑基础内容;组合逻辑电路;各种时序逻辑处理模块的基本原理和实现方法;FPGA设计和硬件描述语言的背景知识及其使用;机器指令中涉及的各类基本运算的运算方法以及相应的运算部件;指令系统的设计;CPU的基本功能和基本结构;各类存储器的工作原理和组织形式;系统互连。

作者简介

数字逻辑电路与计算机组成融会贯通之作

从门电路、基本元件、功能部件到微架构循序渐进阐述硬件设计原理

以新兴开放指令集架构RISC-V为模型机

通过大量图示并结合Verilog语言清晰阐述电路设计思路

从门电路、基本元件、功能部件到微架构循序渐进阐述硬件设计原理

以新兴开放指令集架构RISC-V为模型机

通过大量图示并结合Verilog语言清晰阐述电路设计思路

相关推荐