书籍详情

![《手把手教你RISC-VCPU处理器设计》[31M]百度网盘|亲测有效|pdf下载](/uploads/s0309/11116752c23749be.jpg)

![《手把手教你RISC-VCPU处理器设计》[31M]百度网盘|亲测有效|pdf下载](/uploads/s0309/11116752c23749be.jpg)

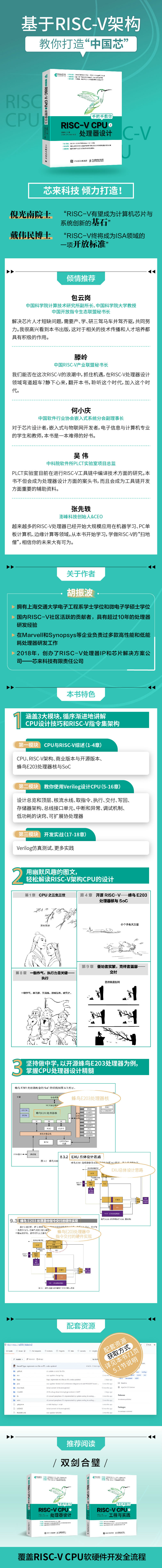

手把手教你RISC-VCPU处理器设计

- 出版社:人民邮电出版社

- 出版时间:2021-10

- 热度:8242

- 上架时间:2024-06-30 09:38:03

- 价格:9.0

免责声明

本站支持尊重有效期内的版权/著作权,所有的资源均来自于互联网网友分享或网盘资源,一旦发现资源涉及侵权,将立即删除。希望所有用户一同监督并反馈问题,如有侵权请联系站长或发送邮件到ebook666@outlook.com,本站将立马改正

内容介绍

产品特色

编辑推荐

1.《手把手教你设计CPU——RISC-V处理器篇》延续篇,配套新蜂鸟E203开源项目,加入更多新内容。

2.利用通俗易懂的语言剖析了RISC-V处理器的微架构以及代码实现,为读者揭开CPU设计的神秘面纱。

3.知识体系完整,分为上下两册,覆盖RISC-V处理器软硬件开发的全流程。

4.中国工程院院士倪光南、芯原股份董事长戴伟民为本书作序推荐。

2.利用通俗易懂的语言剖析了RISC-V处理器的微架构以及代码实现,为读者揭开CPU设计的神秘面纱。

3.知识体系完整,分为上下两册,覆盖RISC-V处理器软硬件开发的全流程。

4.中国工程院院士倪光南、芯原股份董事长戴伟民为本书作序推荐。

内容简介

本书系统地介绍了 CPU 设计技巧和新兴开源RISC-V架构,内容翔实,涵盖开源蜂鸟E203处理器各模块的具体实现,以及可扩展协处理器的实现机制。为了让读者学以致用,本书还集成了大量的实例,用实例把各个模块的实现方式贯穿起来。

本书适合从事CPU设计的工程师和技术爱好者阅读。

本书适合从事CPU设计的工程师和技术爱好者阅读。

作者简介

胡振波,芯来科技创办人兼执行官,中国RISC-V领域的先行者,拥有丰富的处理器内核开发经验,曾长期就职于外企,担任处理器内核研发核心岗位负责人。其打造的国内RISC-V开源项目——蜂鸟E203,对国内RISC-V的普及和推广起到了巨大的推动作用。以胡振波为核心创办的芯来科技目前已经成为中国先行的RISC-V处理器内核IP和解决方案公司,推出的嵌入式CPU核系列产品处于中国RISC-V处理器研发与产业化的前列。